AI Image Processing & Chipset

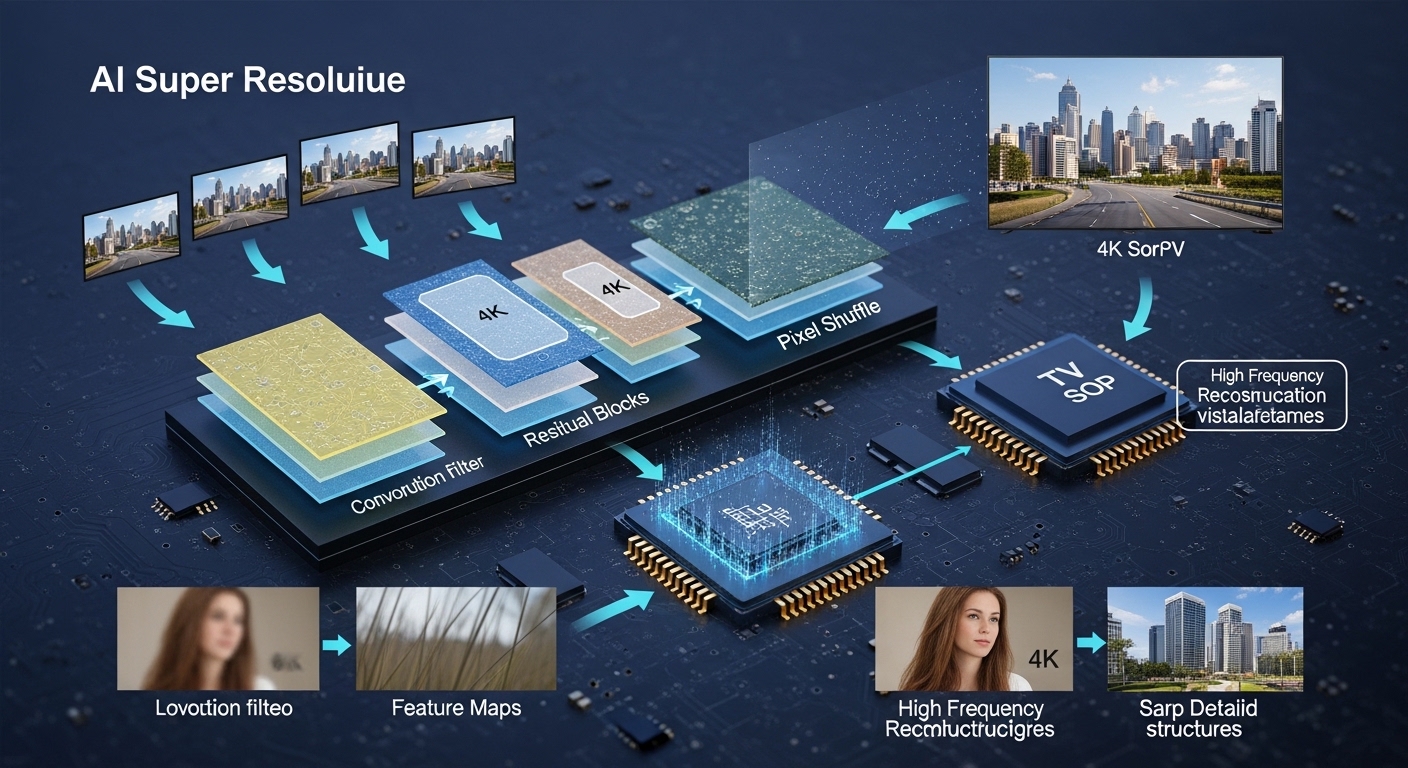

Neural network-based image enhancement, super-resolution algorithms, and processor architectures.

An in-depth engineering analysis of single-image and multi-frame super resolution, CNN architectures (ESRGAN), and real-time upscaling constraints in consumer SoCs.

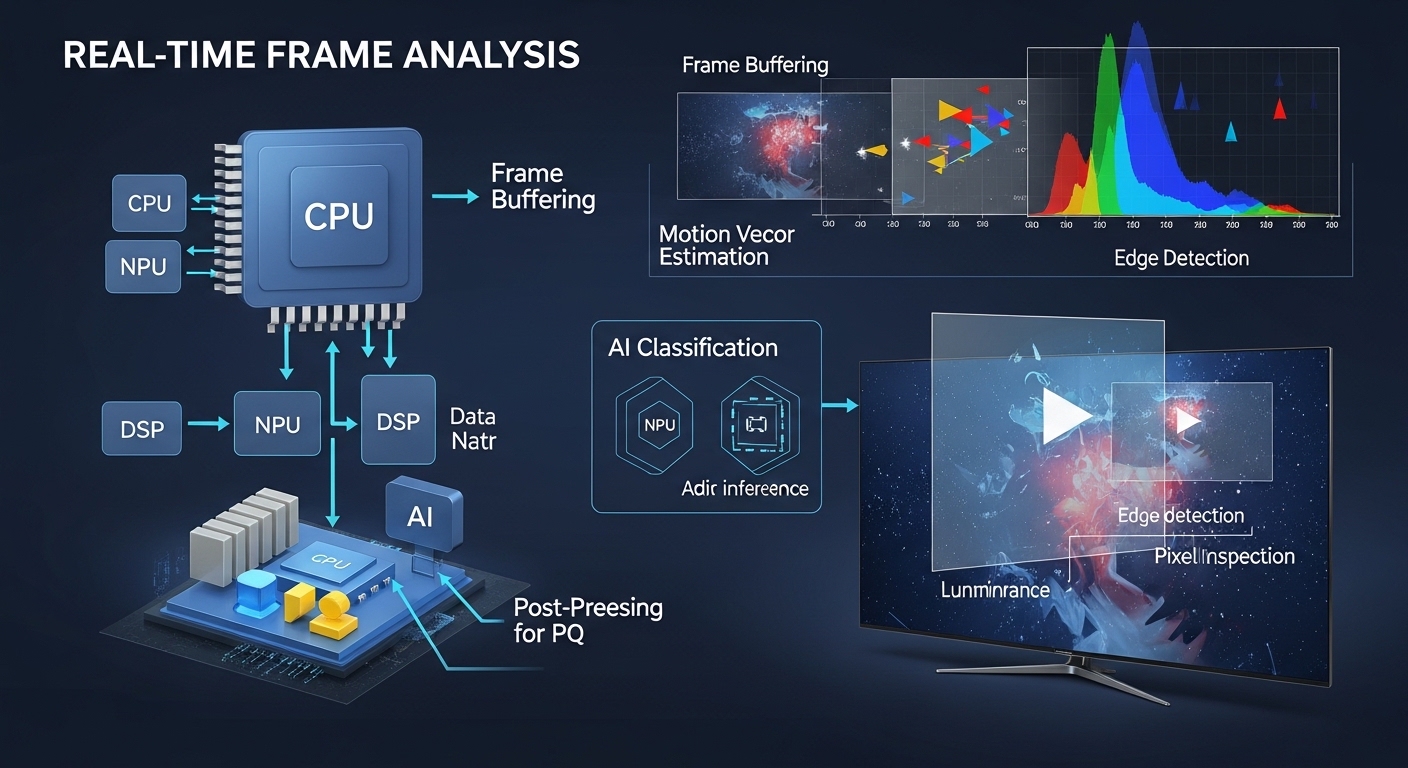

Comprehensive analysis of neural network-based image signal processing, scene detection pipelines, and real-time tone mapping architectures in modern display SoCs.

A comprehensive engineering analysis of real-time video signal processing, covering motion vector estimation, scene classification, histogram analysis, and NPU-driven inference within strict latency budgets.

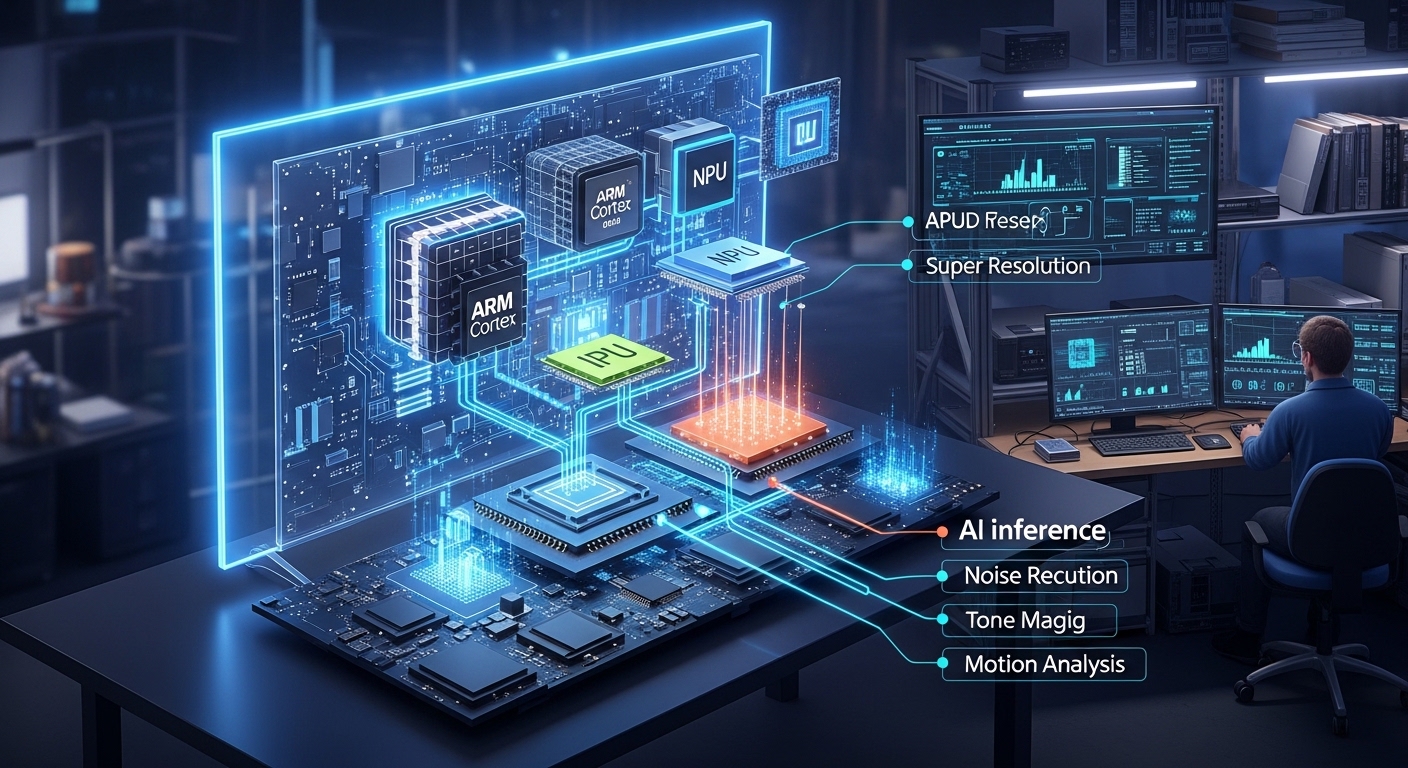

Technical analysis of System-on-Chip (SoC) architectures for TVs, focusing on NPU integration, real-time inference constraints, and heterogeneous computing pipelines.

A rigorous engineering analysis of video denoising algorithms, contrasting traditional spatial-temporal filtering with modern Convolutional Neural Network (CNN) architectures and their real-time implementation in TV SoCs.

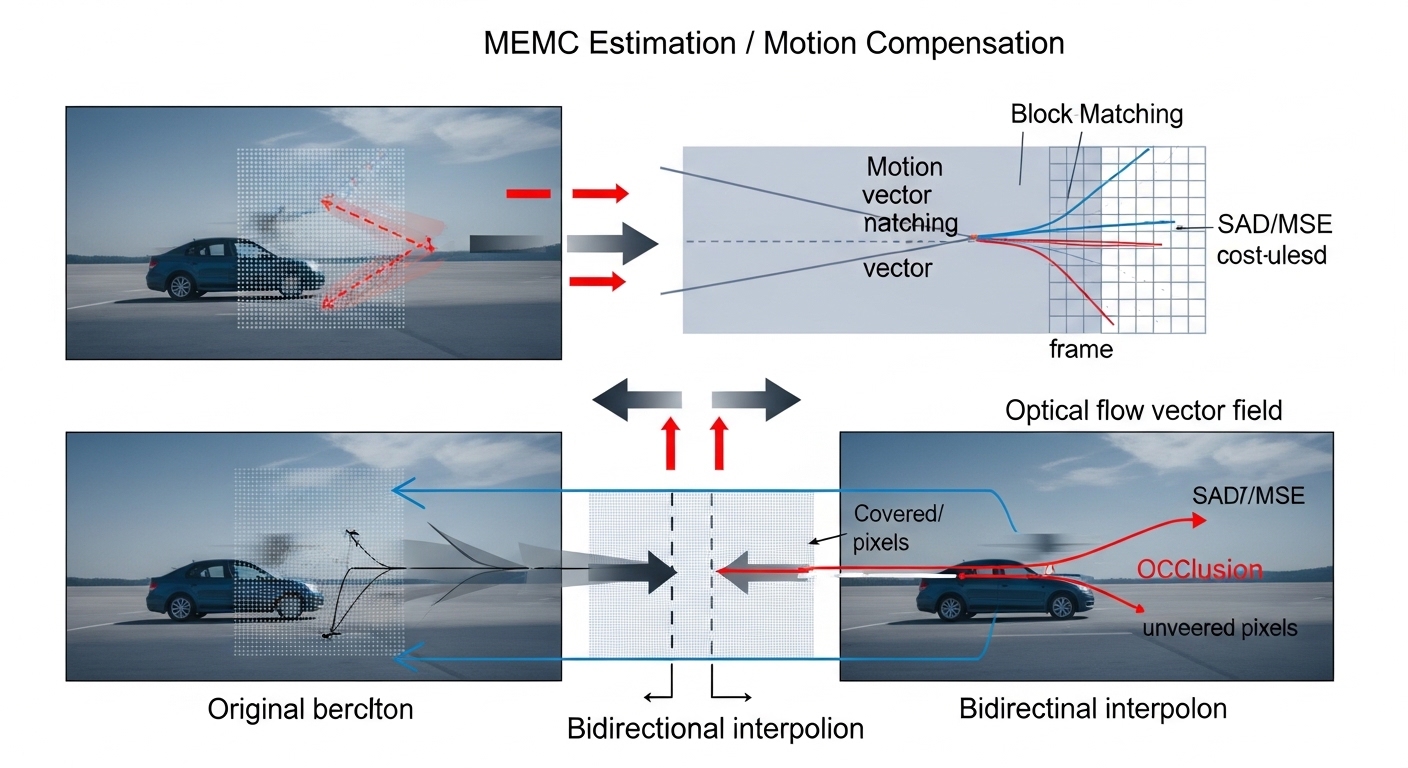

A rigorous mathematical derivation of Motion Estimation/Motion Compensation (MEMC) algorithms, covering Optical Flow constraints, block matching cost functions (SAD/MSE), and the temporal interpolation physics governing modern display engines.